全部

▼

搜索

熱搜:

位置:中冶有色 >

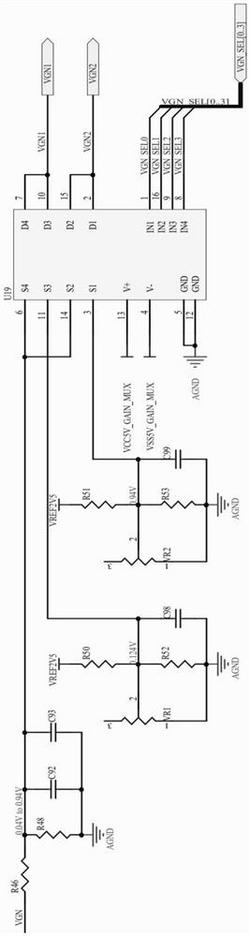

> 超聲波探傷儀的增益控制電路

400

編輯:管理員

來源:青島漢泰智能科技有限公司

400

編輯:管理員

來源:青島漢泰智能科技有限公司

分享 0

分享 0

舉報(bào) 0

舉報(bào) 0

收藏 0

收藏 0

反對 0

反對 0

點(diǎn)贊 0

點(diǎn)贊 0

中冶有色技術(shù)平臺

中冶有色技術(shù)平臺 2025年01月03日 ~ 05日

2025年01月03日 ~ 05日  2025年01月03日 ~ 05日

2025年01月03日 ~ 05日  2025年01月03日 ~ 05日

2025年01月03日 ~ 05日  2025年01月03日 ~ 05日

2025年01月03日 ~ 05日  2025年03月25日 ~ 27日

2025年03月25日 ~ 27日